ASM2P20807A Overview

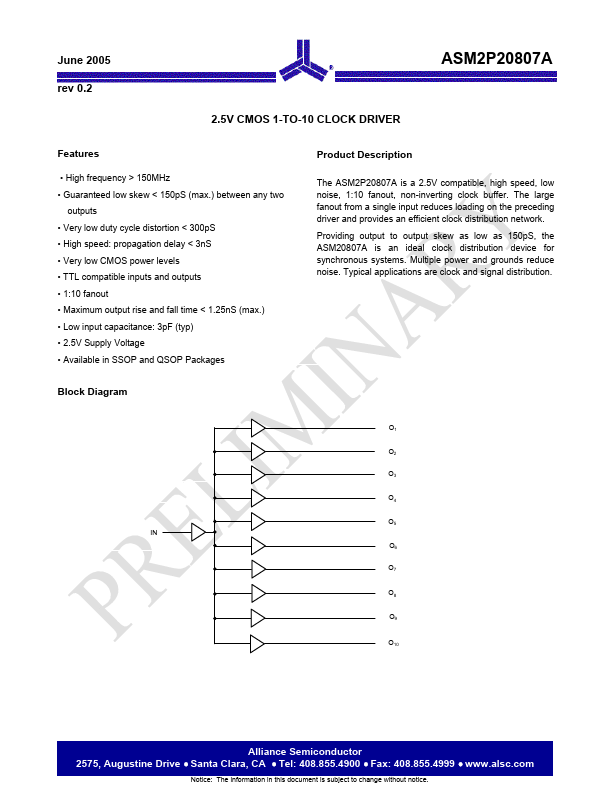

The ASM2P20807A is a 2.5V patible, high speed, low noise, 1:10 fanout, non-inverting clock buffer. The large fanout from a single input reduces loading on the preceding driver and provides an efficient clock distribution network. Providing output to output skew as low as 150pS, the ASM20807A is an ideal clock distribution device for synchronous systems.

ASM2P20807A Key Features

- High frequency > 150MHz

- Guaranteed low skew < 150pS (max.) between any two

- Very low duty cycle distortion < 300pS

- High speed: propagation delay < 3nS

- Very low CMOS power levels

- TTL patible inputs and outputs

- 1:10 fanout

- Maximum output rise and fall time < 1.25nS (max.)

- Low input capacitance: 3pF (typ)

- 2.5V Supply Voltage